Introduction

# 1

# **Table of Contents**

| 1.1  | Library Description                                | 1-1  |

|------|----------------------------------------------------|------|

| 1.2  | Features                                           | 1-2  |

| 1.3  | EDA Support                                        | 1-4  |

| 1.4  | Product Family                                     | 1-4  |

|      | 1.4.1 Analog Core Cells                            | 1-4  |

|      | 1.4.2 Internal Macrocells                          | 1-12 |

|      | 1.4.3 Compiled Macrocells                          | 1-12 |

|      | 1.4.4 Input/Output Cells                           | 1-14 |

| 1.5  | Timings                                            | 1-16 |

| 1.6  | Delay Model                                        | 1-22 |

| 1.7  | Testability Design Methodology                     | 1-24 |

| 1.8  | Maximum Fanouts                                    | 1-27 |

| 1.9  | Packages Capability by Lead Count                  | 1-34 |

| 1.10 | Power Dissipation                                  | 1-36 |

| 1.11 | $V_{\text{DD}}/V_{\text{SS}}$ Rules and Guidelines | 1-39 |

| 1.12 | Crystal Oscillator Considerations                  | 1-45 |

|      |                                                    |      |

| SEC ASIC offers STD110 as 0.25um CMOS standard cell library. SEC's 0.25um cell-based logic process providing up to 5 layers of interconnect metal with various I/O pad-pitch options such as 70um pitch pad and 80um pitch pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STD110 which reduced power dissipation and system cost by merging the logic<br>and IPs as a whole and connecting internally from logic to memory data bus is<br>ideal for high-performance products such as graphics controller, projector,<br>portable CD and so on.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| STD110 can support up to eight million gate counts of logic providing 75% of usable gate. STD110 is 25% faster than 0.35um library MDL90. Logic density is 2.3 times greater than that of MDL90. The power consumption of compiled memory is 90% smaller than MDL90.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| STD110 also supports fully user-configurable compiled memory and datapath elements. Each element is provided as a compiler. Two different types of compiled memories in STD110 are available to support memories suitable to high-density and low-power applications.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| To support mixed voltage environments, 2.5V, 3.3V drive and 5V-tolerant IO cells are available. LVTTL, LVCMOS, PCI, OSC, AGP, PECL, HSTL, LVDS and USB buffers are supported. To better support a system-on-chip design style, various core cells are available including processor cores like ARM7TDMI/ARM9TDMI/ ARM920T/ARM940T from ARM, Teaklite and Oak from DSPG.                                                                                                                                                                                                                                                                                                                                      |

| The STD110 supports data transmission and communication core such as USB, IEEE1284 and UART.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| The list of analog core cells includes ADC, DAC, CODEC, LVDS, RAMDAC and PLL with various bits and frequency ranges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SEC design methodology offers an comprehensive timing driven design flow including automated time budgeting, tight floorplan synthesis intergration, powerful timing analysis and timing driven layout. Its advanced characterization flow provides accurate timing data and robust delay models for a 0.25um very deep-submicron technology. Advanced verification methods like static timing analysis and formal verification provide an effective verification methodology with a variety of simulators and cycle based simulation. SEC DFT methodology supports scan design, BIST and JTAG boundary scan. SEC provides a full set of test-ready IPs with an efficient core test integration methodology. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.2<br>Features | <ul> <li>2.5V standard cell library including processor and analog cores</li> <li>0.25um five layer metal(from four layer metal option) CMOS technology <ul> <li>Logic, processor and analog</li> </ul> </li> <li>High basic cell usages <ul> <li>Up to 8 million gates</li> <li>Maximum usage: 75% for five layer metal</li> </ul> </li> <li>High speed <ul> <li>Typical 2-input NAND gate delay (ND2D4): 70ps (F/O=2 + WL (0.02pF))</li> </ul> </li> <li>Operation temperature (T<sub>A</sub>) <ul> <li>Commercial range: 0°C to +70°C</li> <li>Industrial range: -40°C to +85°C</li> </ul> </li> <li>Digital cores usages <ul> <li>Hard-macro: ARM7TDMI, ARM9TDMI, ARM920T, ARM940T, Oak, Teaklite</li> <li>Soft-macro: AMBA, DMA Controller, SDRAM Controller, Interrupt Controller, IIC, WDT, RTC, USB, IrDA, UART(16C450, 16C550), Fast Ethernet MAC, P1394a LINK, RS Decoder, Viterbi Decoder</li> </ul></li></ul> |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | <ul> <li>Analog cores usages         <ul> <li>Ultra low voltage analog core (2.5V and 1.8V) available</li> <li>Analog core supply voltage:</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 | <ul> <li>Fully user-configurable Static RAMs and ROMs <ul> <li>High-density and low-power memory available</li> <li>Duty-free cycle in synchronous memory available</li> <li>2-bank architecture available</li> <li>Flexible aspect ratio available</li> <li>Up to 256K-bit single-port SRAM available.</li> <li>Up to 128K-bit dual-port SRAM available.</li> <li>Up to 512K-bit diffusion and metal-2 ROM available.</li> <li>Up to 16K-bit multi-port register file available.</li> <li>Up to 32K-bit FIFO available.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                           |

|                 | <ul> <li>Fully configurable datapath macrocells <ul> <li>4 ~ 64 bit adder available</li> <li>4 ~ 64 bit barrel shifter available</li> <li>6 ~ 64 bit multiplier with 1-stage pipeline available</li> <li>Various output driver strength available</li> <li>A tightly integrate apollo, Avant!, design environment</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | <ul> <li>I/O cells         <ul> <li>2.5V/3.3V and 5V tolerant IO</li> <li>3-level (high, medium, no) slew rate control</li> <li>1/2/4/6/8/10/12mA available for 3.3V and 2.5V output buffers</li> <li>1/2/3mA available for 5V-tolerant output buffers</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

- 1/2/3mA available for 5V-tolerant output buffers

- IO IP available

- PCI ((33MHz, 66MHz, 3.3V), (33MHz, 3.3/5V tolerant))

- USB (full speed/low speed)

- SSTL2 (DDR SDRAM interface, up to 200MHz)

- AGP (AGP2.0 Compliant, 66MHz@1X,133MHz@2X, 266MHz@4X)

- PECL (2.5V interface, up to 400MHz)

- HSTL (class1, class2, 30MHz)

- LVDS (3.3V(2.5V optional) interface, 300MHz)

- Various package options

- QFP, thin QFP, power QFP, plastic BGA, super BGA, plastic leaded chip carrier, etc.

- Fully integrated CAD software and EDA support

- Logic synthesis: Synopsys Design Compiler

- Logic simulation: Cadence Verilog-XL, Cadence NC-Verilog,

- Viewlogic ViewSim, Mentor ModelSim-VHDL,

Mentor ModelSim-Verilog, Synopsys VSS,

#### Synopsys VCS

- Scan insertion and ATPG: Synopsys TestGen, Synopsys Test Compiler, Mentor Fastscan

- Static timing analysis: Synopsys PrimeTime, Synopsys MOTIVE

- RC analysis: Avant! Star-RC

- Power analysis: Synopsys DesignPower, CubicPower (In-House Tool)

- Formal verification: Synopsys Formality, Chrysalis Design VERIFYer, Verplex Tuxedo-LEC

- Fault simulation: Cadence Verifault, SuperTest (In-House Tool)

- Delay calculator: CubicDelay (In-House Tool)

- STD110 contains 12 user selectable clock tree cells(CTC). At the pre-layout design stage, these will be used as the cells which represent actual clock tree informatin of P&R. The key features of new SEC ASIC CTS flow are as follows:

- 12 user selectable clock tree cells(CTC) for STD110

- Good pre-layout and post-layout correlation

- No customer netlist modification

- Accurate post-layout back-annotation mechanism

- Insertion delay, skew, transition time management

- Clock tree information file generation

- Cover 100 to 30,000 fanouts and up to 1M gate count for CTS spanning block (GCCSB)

- Tightly coupled with SEC in-house delay calculator, CubicDelay Gated CTS support

- Hierarchical/Flatten verilog, edif interface for P&R

For more detail information for CTC flow, refer to "CTC flow guideline for CubicDelay" included in SEC ASIC design kit.

| 1.3<br>EDA Support | SEC ASIC provides an efficient solution for multi-million gate ASICs in very deep<br>submicron (VDSM) technology. For large system-on-chip (SOC) type designs,<br>static verification methodology (static timing analysis and formal verification) will<br>shorten your design cycle time, which in turn will lessen today's ever-increasing<br>time-to-market pressure. Our Design-for-Test (DFT) methodology and service<br>take you through all phases of test insertion, test pattern generation and fault<br>grading to get high test coverage. |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | STD110 supports a rich collection of industry-standard EDA tools from Cadence,<br>Synopsys, Mentor graphics, and Avant! on multiple design platforms such as<br>Solaris and HP. Customers are allowed to choose among the industry-leading<br>EDA tools from design capture, synthesis, simulation, and DFT to layout. Several<br>powerful proprietary software tools are seamlessly integrated in our design kits to<br>improve your product quality.                                                                                               |

|                    | For high simulation accuracy, STD110 uses a proprietary delay calculator. Cell delay is calculated based on a matrix of delay parameters for each macrocell, and signal interconnect delay is calculated based on the RC tree analysis.                                                                                                                                                                                                                                                                                                              |

| 1.4                | STD110 library include the following design elements:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Product Family     | ■ Analog core cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | Digital core cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | Internal macrocells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | Compiled macrocells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | Input/Output cells.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    | 1.4.1 ANALOG CORE CELLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Introduction to Analog Cores

SEC ASIC is one of the leading suppliers of cell based mixed analog and digital designs. As a leading supplier of mixed analog and digital designs, SEC ASIC has more analog design experience than any other vendors. Analog has been and will continue to be a part of the strategic focus at SEC ASIC. Analog design is a part of the total SEC ASIC integrated design system. Workstation symbols are supplied for analog cells and are entered as part of the design by the customer or design center. SEC ASIC uses basically the same automatic layout and verification tools for analog cells as for digital cells. Analog designs are processed on the same production line as digital designs.

SEC's analog core family comprises ADC,DAC,PLL and sigma-delta ADC/DAC, and their brief functional descriptions are introduced below. [data sheets for all analog cores available]

#### Analog-to-Digital Converters

Analog-to-digital converters provide the link between the analog world and digital systems. Due to their extensive use of analog and mixed analog-digital operations, A/D converters often appear as the bottleneck in data processing applications, limiting the overall speed or precision.

An A/D converter produces a digital output, D, as a function of the analog input, A:

D = f(A)

While the input can assume an infinite number of values, the output can be selected from only a finite set of codes given by the converter's output word length(i.e, resolution). Thus, the ADC must approximate each input level with one of these codes, this process is so called 'quantization'.

In a digital system the amplitude is quantized into discrete steps, and at the same time the signal is sampled at discrete time intervals. This time interval is called sampling time or sampling frequency. After sampling and quantization process, the analog signal(A) becomes digital output (D).

#### **Digital-to-Analog Converters**

The D/A converters are the digital-to-analog conversion circuits, which are also called DACs. They can be considered as decoding devices that accept digitally coded signals and provide analog output in the form of currents or voltages. In this manner, they provide an interface between the digital signal of the computer systems and continuous signals of analog world. They are employed in a variety of applications, from CRT display systems and voice sythesizers to automatic test systems, digital controlled attenuators, and process control actuators. In addition, they are key components inside most A/D converters.

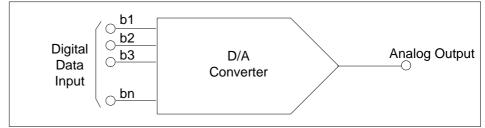

Figure 1 shows the functional block diagram of a basic D/A converter system. The input to the D/A converter is a digital word, made up a stream of binary bits comprised of 1's and 0's. The output analog quantity A, which can be a voltage or current, is related to the input as

$$A = KV_{REF} \left[\frac{b1}{2^1} + \frac{b2}{2^2} + \dots + \frac{bn}{2^n}\right]$$

where K is a scale factor,  $V_{REF}$  is a reference voltage, n is the total number of bits, and b1,b2,...,bn are the bit coefficients, which are quntized to be a 1 or a 0.

As a function of the input binary word which determines the bit coefficients, the output exhibits 2<sup>n</sup> discrete voltage level ranging from zero to a maximum value of

$$Vo(max) = V_{REF} \frac{2^n - 1}{2^n}$$

with a minimum step change  $\Delta Vo$  given as

$$\Delta Vo = \frac{V_{REF}}{2^n}$$

Figure 1-1. Functional Block Diagram of Basic D/A Converter

#### Sigma-Delta ADC/DAC

VLSI offers high speed and high density, but reduced accuracy for analog components and reduced signal range (reduced dynamic range). Hence, an exchange of digital complexity and of resolution in time for resolution in signal amplitude is needed. So good solution is over-sampling data converter. Oversampling sigma-delta converter is used in slow speed (audio band) application because of process limit. It's noise shaping (sigma-delta) feature make high resolution about max. SND=90~100dB

In ADC path, analog single input is converted to differential signal with anti-aliasing filtering through anti-aliasing filter block. And sigma-delta modulator converts the signal into oversampled noise-shaping 1bit PDM (Pulse Density Modulation). Following digital decimation filter reject the out of band noise and outputs 16bits high resolution digital data with down sampled to Fs rate. In DAC path, digital input data is oversampled by interpolation filter and it is converted to noise-shaped 1bit PDM through digital sigma-delta modulator. Analog SC-post-filter rejects the out of band noise. And anti-image filter rejects sampling images and outputs single analog signal with high resolution.

#### Phase Locked Loop

Samsung's PLL cores implemented as an analog function provide frequency multiplication capabilities and enable system designers to synchronize ASIC chip-level clock networks with a common reference signal.

In the past, designers wishing to incorporate a PLL into a digital design environment had only two options:

(1) A special mixed-signal process to incorporate analog functions onto the chip(2) An all digital PLL that can be incorporated into a standard digital process.

However, a mixed-signal process is too expensive to be a feasible solution. On the other hand digital PLLs typically require huge silicon area and exhibits poor locking time despite their high accuracy.

Differing from the previous solutions, Samsung's PLL cores can be implemented on standard digital CMOS process while functioning as an analog PLL.

Samsung's PLL cores:

- \* Require only a few off-chip passive components for the whole function

- \* Remove the need for an expensive mixed-signal process

- \* Provide faster locking time than all digital PLLs

- \* Present low jitter characteristics

#### **Glossary by Core Families**

#### 1. Digital-to-Analog Converter

**1. Resolution** - An n-bit binary converter should be able to provide  $2^n$  distinct and different analog output values corresponding to the set of n-bit binary words. A converter that satisfies this criterion is said to have resolution of n bits. The smallest output change that can be resolved by a linear DAC is  $2^{-n}$  of the full-scale span.

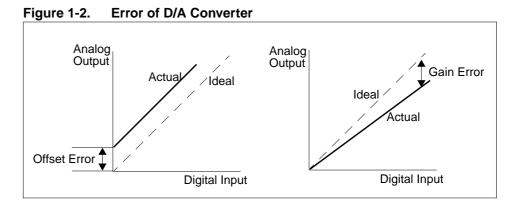

**2.** Accuracy - Error of a D/A converter is the difference between the actual analog output and the output that is expected when a given digital code is applied to the converter. Source of error include gain error, offset error, linearity errors and noise. Error is usually commensurate with resolution, less than  $2^{-(n+1)}$ , or 1/2 LSB of full scale.

*3. LSB (Least-Significant Bit)* - In a system in which a numerical magnitude is represented by a series of binary digits, the LSB is that bit that carries the smallest value or weight. It represents the smallest analog change that can be resolved by an n-bit converter.

LSB (Analog Value) = FSR/2<sup>n</sup>

FSR = Full-Scale Range, n = number of bits

**4. MSB (Most-Significant Bit)** - The binary digit with the largest numerical weighting. Normally, the MSB of a digital word has a weighting of 1/2 the full range.

**5.** Compliance-Voltage Range - For a current output DAC, the maximum range of(output) terminal voltage for which the device will provide the specified current-output characteristics.

**6.** *Glitch* - A glitch is a switching transient appearing in the output during a code transition. Its value is expressed as a product of voltage (V\*ns) or current (mA\*ns) and time duration or charge transferred.

**7. Harmonic Distortion (and Total Harmonic Distortion)** - The DAC is driven by the digitized representation of sine wave. The ratio of the RMS sum of the harmonics of the DAC output to the fundamental value is the THD. Usually only the lower order harmonics are included, such as second through fifth.

THD =

$$20\log \frac{(V2^2 + V3^2 + V4^2 + V5^2)^{1/2}}{V1}$$

V1: RMS amplitude of the fundamental

**8. Signal-to-Noise Ratio (SNR)** - This signal to noise ratio depends on the resolution of the converter and automatically includes specifications of linearity, distortion, sampling time uncertainty, glitches, noise, and settling time. Over half the sampling frequency, this signal to noise ratio must be specified and should ideally follows the theoretical formula;

$$S/N_{max} = 6.02N + 1.76dB$$

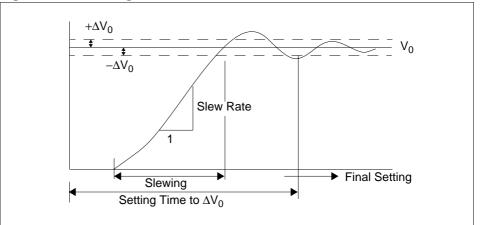

**9.** Slew Rate - Slew rate of a device or circuit is a limitation in the rate of change of output voltage, usually imposed by some basic circuit consideration such as limited current to charge of capacitor. Amplifiers with slew rate of a few V/µs are common and moderate in cost. Slew rates greater than about 75 V/µs are usually seen only in more sophisticated (and expensive) devices The output slewing speed of a voltage-output D/A converter is usually limited by the slew rate of the amplifier used at its output (if one is used).

**10. Settling Time** - The time required, following a prescribed data change from the 50% point of the login input change, for the output of a DAC to reach and to remain within a given fraction (usually  $\pm 1/2$ lsb) of the final value. Typical prescribed changes are full scale, 1MSB and 1LSB at a major carry. Settling time of current-output DACs is quite fast. The major share of settling time of a voltage-output DAC is usually contributed by the settling time of the output op-amp circuit.

Figure 1-3. Setting Time

**11.** *Power-Supply Sensitivity* -The sensitivity of a converter to changes in the power-supply voltages is normally expressed in terms of percent-of-full-scale change in analog output value (of fractions of 1LSB) for a 1% dc change in the power supply. Power supply sensitivity may also expressed in relation to a specified dc shift of supply voltage. A converter may be considered "good" if the change in reading at full scale does not exceed 1/2LSB for 3% change in power supply. Even better specs are necessary for converters designed for battery operation.

**12. ILE (integral Linearity Error)** - Linearity error of a converter, expressed in %, ppm of full-scale range or multiples of 1LSB, is a deviation of the analog values in a plot of the measured conversion relationship from a straight line. The straight line can be either a "best straight line" determined empirically by manipulation of the gain and/or offset to equalize maximum positive and negative deviation of the actual transfer characteristics from this straight line; or it can be a straight line passing through the endpoints of the transfer characteristic after they have been calibrated (sometimes referred to as "endpoint" linearity). Endpoint linearity error is similar to relative accuracy error. For multiplying D/A converters, the analog linearity error, at a specified digital code, is defined in the same way as for multipliers, by deviation from a "best straight line" through the plot of the analog output-input response.

**13. DLE (Differential Linearity Error)** - Any two adjacent digital codes should result in measured output values that are exactly 1LSB apart (2-n of full scale for an n-bit converter). Any deviation of the measured "step" from the ideal difference is called differential linearity error expressed in multiplies of 1LSB. It is an important specification because a differential linearity error greater than 1LSB can lead to non-monotonic response in a D/A converter and missed codes in an A/D converter.

**14. Monotonic** - A DAC is said to be monotonic if the output either increases or remains constant as the digital input increases with the result that the output will always be a single-valued function of the input. The specification "monotonic"

(over a given temperature range) is sometimes substituted for a differential nonlinearity specification since differential nonlinearity less than 1LSB is a sufficient condition for monotonic behaviour.

#### 2. Analog-to-Digital Converter

**1. ILE (Integral Linearity Error: INL)** - Integral nonlinearity refers to the deviation of each individual code from a line drawn from "zero" through "full scale". The point used as "zero" occurs 1/2LSB before the first code transition. "Full scale" is defined as a level 1 1/2LSB beyond the last code transition. The deviation is measured from the center of each particular code to the true straight line.

**2. DLE (Differential Linearity Error: DNL)** - An ideal ADC exhibits code transitions that are exactly 1LSB apart. DNL is the deviation from this ideal value. It is often specified in terms of the resolution for which no missing codes are guaranteed.

**3.** Offset Error - The first transition should occur at a level 1/2LSB above "zero". Offset is defined as the deviation of the actual first code transition from that point.

**4. Gain Error** - The first code transition should occur for an analog value 1/2LSB above nominal negative full scale. The last transition should occur for an analog value 1 1/2LSB below the nominal positive full scale. Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between the first and last code transitions.

**5.** *Pipeline Delay (Latency)* - The number of clock cycles between conversion initiation and the associated output data being made available. New output data is provided every clock cycle.

**6. Effective Number of Bits (ENOB)** - This is a measure of a device's dynamic performance and may be obtained from the SNDR or from a sine wave curve test fit according to the following expression:

ENOB = SNDR - 1.76/6.02

ENOB = N-log2[RMS error (actual) / RMS error (ideal)]

**7. Analog Bandwidth** - The analog input frequency at which the spectral power of the fundamental frequency, as determined by FFT analysis is reduced by 3dB.

**8.** Aperture Delay - The delay between the sampling clock and the instant the analog input signal is sampled.

9. Aperture Jitter - The sample to sample variation in aperture delay.

**10.** *Bit Error Rate (BER)* - The number of spurious code errors produced for any given input sine wave frequency at a given clock frequency. In this case it is the number of codes occurring outside the histogram cusp for a 1/2 FS sine wave.

**11. Signal to Noise Ratio** - This signal to noise ratio depends on the resolution of the converter and automatically includes specifications of linearity, distortion, sampling time uncertainty, glitches, noise, and settling time. Over half the sampling frequency, this signal to noise ratio must be specified and should ideally follow the theoretical formula;

$$S/N_{max} = 6.02N + 1.76dB$$

#### 3. Phase Locked Loop

**1. Lock Time** - The time it takes the PLL to lock onto the system clock. Fast or slow lock time may be controlled by the loop filter characteristics. The loop filter characteristics are controlled by varying the R and C components. (Remember that R and C define the damping-factor as well)

**2. Phase Error** - The phase difference between the feedback clock signal and the system signal clock.

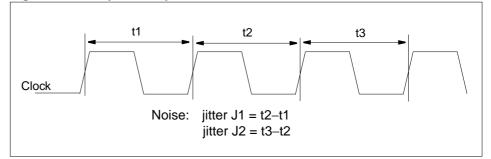

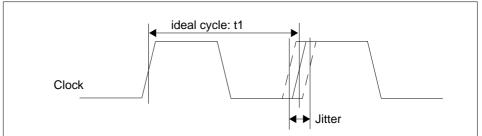

**3.** Clock Jitter - The deviations in a clock's output transitions from their ideal positions define the clock jitter. Jitter is sometimes specified as an absolute value in nanoseconds. All jitter measurement are made at a specified voltage.

1) Cycle-to-Cycle Jitter: The change in a clock's output transition from its corresponding position in the previous cycle. This kind of jitter is the most difficult to measure and usually requires a time-interval analyzer

Figure 1-4. Cycle-to-Cycle Jitter

: The maximum of such values over multiple cycles (J1,J2...) is the max. cycle-to-cycle jitter.

2) Period Jitter: Period jitter measures the maximum change in a clock's output transition from its ideal position. You can use period-jitter measurements to calculate timing margins in systems.

#### Figure 1-5. Period Jitter

3) Long-term Jitter: Long-term jitter measures the maximum change in a clock's output transition from its ideal position over many cycles. How many cycles depends on the application and the frequency. A classic example of system affected by long-term jitter is a graphics card driving a CRT

4) Power Down Mode: PLL state in which the quiescent current is lowered to a very low level to conserve power.

5) Synthesize clock: a system clock may run at a relatively low rate compared to system components. A CPU, for example, may require an internal clock that is several times faster than the system I/O bus clock. Designers can use PLL

technology to synthesize a higher frequency on-chip clock using the system clock as a reference.

6) Deskew clock: Multiple chips on a printed circuit board or cores of different sizes within a single system on a chip experience clock skew. By using PLL or DLL technology to shift the phase of the reference clock within each chip or core, designers can minimize skew tune a system to perform up its potential.

7) Duty Ratio: the percentage of the period that the output is in a high state.

8) Output frequency range: The maximum output frequency range minus the minimum output frequency that is produced with an input signal for which the cell specifications still apply.

#### **Customer Service**

SEC provides a full custom support for our customers need of analog cores. SEC's worldwide sales offices and representatives give our customers a firsthand support for analog cores. And if needed, SEC engineers are prepared to provide a fully customized total solution to satisfy our customers.

#### **Technical Support**

If our customers want to develop mixed-signal products, SEC provides all technical support to meet customers needs. Mixed-signal design is quite different from pure logic design in terms of circuit design, techniques, layout and test methodology. Thus SEC provides a successful technical guide and firmly support for all development steps.

#### **Definition of Analog Core Data Sheet Types**

Each product developed by SEC will be supported by technical literature where the data sheets progress through the following levels of refinement

#### 1. Core Preview

Describes the main features and specifications for core that is under development. Some specifications such as exact pin-outs may not be finalized at time of publication. The purpose of this document is to provide customers with advance product planning information.

#### 2. Preliminary Datasheet

This is the first document completely describing a new core. It contains an features, application, timing diagram, theory of operation, core pin information, test guide, layout guide and AC/DC electrical information. This data sheet are based on prototype silicon performance and on worst case simulation models. The purpose of this data sheet is to provide ASIC customer with technical information sufficiently detailed to guarantee that they can safely begin active development.

#### 3.Final Data sheet

This is an updated version of preliminary data sheet reflecting actual performance of the final silicon. Updates include tighter specifications, more min. and max. values. The purpose of this data sheet is to communicate the confirmed performance of cores which have passed qualification, been fully characterized.

#### 1.4.2 INTERNAL MACROCELLS

Internal Macrocells are the lowest level of logic functions such as NAND, NOR and flip-flop used for logic designs. There are about 471 different types of internal macrocells. They usually come in four levels of drive strength (0.5X, 1X, 2X and 4X).

These macrocells have many levels of representations—logic symbol, logic model, timing model, transistor schematic, HSPICE netlist, physical layout, and placement and routing model.

#### 1.4.3 COMPILED MACROCELLS

Compiled macrocells of STD110 consist of compiled memory and compiled datapath macrocells.

#### 1.4.3.1 Compiled Memory Macrocells

Memories in STD110 are fully user-configurable and are provided as a compiler. Two different types of memories are available in STD110. One is suitable for highdensity application with high-performance, called STD110-HD compiled memory. The other is suitable for low-power application, called STD110-LP compiled memory.

In STD110-HD compiled memory, eight types of memories are available such as single-port synchronous/asynchronous static RAM, dual-port synchronous static RAM, synchronous diffusion/metal-programmable ROM, multi-port asynchronous register file and synchronous first-in first-out memory. Synchronous memories have a fully synchronous operation at the rising-edge of clock and the duty-free cycle is available. Also, the bit-write capability is available. Asynchronous memories have a synchronous operation for a write enable signal during write mode and have an asynchronous operation for address signal during read mode. Multi-port asynchronous register file supports four kinds of configurations such as 2 port(1-read/1-write), 3 port(1-read/2-write and 2-read/1-write) and 4 port (2-read/2-write). The first-in first-out memory which is widely used in communication buffering types of applications has also fully synchronous operation at the rising- edge of clock.

On the other hand, in STD110-LP compiled memory, five types of memories are available such as single-port synchronous/asynchronous static RAM, dual-port synchronous static RAM and synchronous diffusion/metal-programmable ROM. Synchronous memories are almost same as that of STD110-HD except that the duty-free cycle is not available. Asynchronous memory is same as that of STD110-HD.

To dramatically reduce the power consumption in STD110-LP, some of lowpower techniques such as a partial activation architecture in cell array and a divided word-line structure was adopted, rather than STD110-HD.

Basically in STD110-HD and STD110-LP, the power-down mode which significantly reduces the power dissipated during a read or write mode is provided. Also compiled memories have a standby mode except multi-port asynchronous register file and first-in first-out memory. While in standby mode, the data stored in the memory is retained, data outputs remain stable and the power is greatly reduced because memory operation is internally blocked while the memory contents and the data outputs are unaffected. To improve the memory performance and to reduce the power consumption, 2bank architecture is provided except some memories such as dual-port synchronous static RAM, multi- port asynchronous register file and first-in first-out memory. In 2-bank architecture, only one bank is activated and the other bank is in standby mode.

To support various memory shapes which are determined by the floorplan of a chip design, flexible memory aspect ratios are provided. For certain specific memory configuration, all types of timing, power and area values are provided by an automatic datasheet generator.

To easily do interface to layout, the physical abstract data for Silicon Ensemble and Apollo, called phantom cell or black box, is provided. BIST(Built-In Self-Test) circuitry is currently available for most of STD110 compiled memories. BIST circuits are designed to detect a set of fault types that impact the functionality of memory and is generated by a softmacro-based BIST generator.

The softmacro-based BIST generator generates both an individual BIST netlist for each memory and a shared BIST netlist for all memories used in a design. However, when several memories of the same or the different type area used in the design, if you generate the individual BIST netlist for each memory, there are some redundant blocks because the individual BIST netlist has same function. In this case, it would better use the shared BIST netlist to eliminate such redundancy and reduce area.

#### 1.4.3.2 Compiled Datapath Macrocells

Compiled datapath macro cells include Adder, Barrel Shifter and Multiplier. Adder performs the adding or adding/subtracting operation on the control of a mode selection signal. Barrel Shifter makes input data shift or rotate in the left/right direction. In the shift operation, the vacant bit can be padded with zero, MSB value, or external data. Multiplier performs the 2's compliment multiplication. One pipeline stage insertion is available to get a high operating frequency.

They have two output drive strengths, which are equal to the 1X and 2X-Drive in the primitive cell library. The hard macro cells are built through the Apollo, placement and routing tool from Avant!. All the leaf cells have the same physical configuration compatible with the primitive cell library. It allows that any primitive cell can be used as a bit slice cell in the datapath module design.

We provide two kinds of engineering design services. One is to support additional compiled datapath macrocells such as ALUs, Comparators, Priority encoders, Incrementers and Decrementers, and so on. Another is to make hardwired datapath module design which provides a regular structured layout.

#### 1.4.4 INPUT/OUTPUT CELLS

There are about seven hundreds different I/O buffers. Each I/O cell is implemented solely on the basic I/O cell architecture which forms the periphery of a chip.

A test logic is provided to enable the efficient parametric (threshold voltage) testing on input buffers including LVCMOS and TTL level converters, Schmitt trigger input buffers, clock drivers and oscillator buffers. Pull-up and pull-down resistors are optional features.

Three basic types of output buffers (non-inverting, tri-state and open drain) are available in a range of driving capabilities from 1mA to 12mA for 2.5V, 3.3V drive and from 1mA to 3mA for 5.0V tolerant drive. One or two levels of slew rate controls are provided for each buffer type (except 1mA, 2mA and 3mA buffers) to reduce output power/ground noise and signal ringing, especially in simultaneous switching outputs.

Bi-directional buffers are combinations of input buffers and output buffers (tristate and open drain) in a single unit. The I/O structure has been fully characterized for ESD protection and latch-up resistance.

For user's convenience, STD110 library provides  $100K\Omega$  pull-down and pull-up resistance respectively.

#### 1.4.4.1 I/O Applications

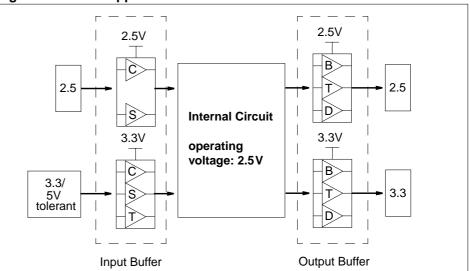

To support mixed voltage environments, LVTTL, LVCMOS and Schmitt trigger I/ O cells are available at 2.5V, 3.3V interface and 5V tolerant interface. The I/O application diagram is as follows.

Figure 1-6. I/O Applications

#### 1.4.4.2 I/O Cell Drives Options

To provide designers with the greater flexibility, each I/O buffer can be selected among various current levels (e.g., 1mA, 2mA,..., 12mA). The choice of current-level for I/O buffers affects their propagation delay and current noise.

The slew rate control helps decrease the system noise and output signal overshoot/undershoot caused by the switching of output buffers. The output edge rate can be slowed down by selecting the high slew rate control cells.

STD110 provides three different sets of output slew rate controls. Only one I/O slot is required for any slew rate control options.

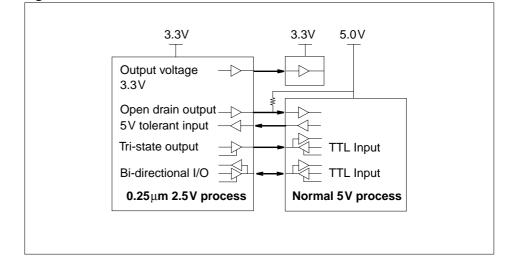

#### 1.4.4.3 5V Tolerant I/O Buffers

STD110 I/O library is based on a process which has the most optimum performance in 2.5V.

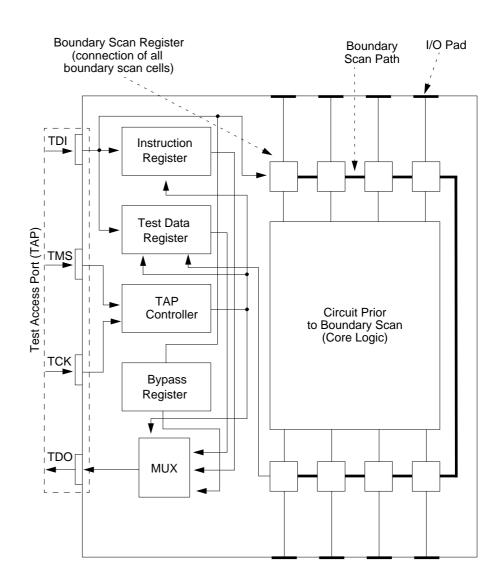

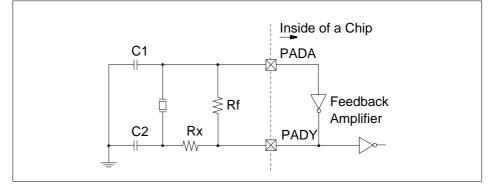

In this process, voltage more than 3.6V are not allowed at the gate oxide because of a reliability problem. And a special circuit is adopted in order to make pin voltage tolerable up to 5.25V and to offer TTL interface driving up to 3mA. Obviously, this circuit is constructed not to permit more than 3.6V at the gate oxide. The external circuit diagram is as follows.

The maximum external tolerance of this buffer is 5.25V. It can be used as a 3.3V normal buffer.

Figure 1-7. 5V Tolerant I/O Buffers

#### 1.4.4.4 PCI Buffers

PCI buffers are designed for PCI local bus application which is an industrystandard, high-performance 32bit or 64bit bus architecture. SEC ASIC offers input, output, bi-directional PCI buffers for 33MHz and 66MHz operation. These buffers are compliant with PCI local bus specification 2.1.

#### 1.4.4.5 USB (Universal Serial Bus) Buffers

Various kinds of peripheral equipment such as mouse, joy stick, keyboard, modem, scanner and printer improve the power of a computer. However, it is not easy to connect and use them properly in the computer.

USB specification established late in 1995 is a good solution for this problem, providing facile method of an expansion. SEC ASIC offers full speed and low speed USB buffers that complies with Universal Serial Bus specification 1.0, 1.1.

#### 1.4.4.6 Other Buffers

SEC ASIC can support various kinds of buffers such as HSTL, SSTL, AGP, PECL, LVDS, and so on. For more information please contact us.

## 1.5 Timings

#### 1.5.1 WIRE LENGTH LOAD

Table 1-1. shows the equivalent standard load matrix for 4-layer and 5-layer metal interconnect. The equivalent standard load values are function of gate count and fanout. These values are based on capacitive loading and are used in wire length estimates which affect propagation delay.

Table 1-1.

Equivalent Standard loads for 4-layer and 5-layer Metal Interconnect

| Gates   |        |         |         |         |         | Fanouts |         |         |         |         |         |

|---------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Count   | 1      | 2       | 3       | 4       | 5       | 6       | 7       | 8       | 16      | 32      | 64      |

| 4LM     | 11     | 1       | 1       | I       | I       | 1       | I       | 1       | I       | 1       |         |

| 5000    | 1.159  | 2.242   | 3.822   | 5.113   | 5.965   | 7.020   | 7.859   | 10.94   | 28.672  | 45.642  | 79.821  |

| 10000   | 1.530  | 2.932   | 5.561   | 7.701   | 8.964   | 10.500  | 12.110  | 15.211  | 29.903  | 47.725  | 83.520  |

| 50000   | 4.192  | 8.247   | 12.439  | 16.494  | 16.801  | 17.980  | 21.026  | 22.806  | 35.536  | 48.347  | 84.605  |

| 100000  | 4.596  | 9.327   | 13.925  | 18.523  | 18.889  | 20.241  | 23.582  | 27.031  | 41.002  | 54.253  | 94.944  |

| 150000  | 12.843 | 17.125  | 21.406  | 22.684  | 23.600  | 24.296  | 26.001  | 29.730  | 39.828  | 63.672  | 127.344 |

| 200000  | 13.520 | 18.026  | 22.533  | 23.885  | 24.849  | 25.582  | 27.372  | 31.299  | 41.865  | 66.931  | 133.812 |

| 300000  | 14.871 | 19.830  | 24.786  | 26.588  | 27.596  | 28.363  | 30.317  | 34.634  | 46.268  | 73.871  | 147.587 |

| 400000  | 16.225 | 21.631  | 26.852  | 28.693  | 29.845  | 30.718  | 32.868  | 37.479  | 50.016  | 79.707  | 159.207 |

| 500000  | 18.099 | 24.132  | 30.166  | 32.177  | 33.435  | 34.390  | 36.777  | 42.032  | 53.235  | 84.861  | 169.459 |

| 600000  | 19.375 | 25.836  | 32.476  | 34.593  | 35.915  | 36.919  | 39.467  | 45.186  | 54.763  | 87.312  | 174.320 |

| 800000  | 22.324 | 29.767  | 37.739  | 40.113  | 41.593  | 42.719  | 45.642  | 52.399  | 59.180  | 94.390  | 188.385 |

| 1000000 | 25.078 | 33.439  | 42.657  | 45.272  | 46.898  | 48.140  | 51.408  | 59.135  | 63.283  | 100.964 | 201.447 |

| 1500000 | 32.631 | 43.509  | 56.047  | 59.341  | 61.381  | 62.946  | 67.174  | 77.514  | 75.639  | 120.743 | 240.788 |

| 2000000 | 39.706 | 52.941  | 68.596  | 72.524  | 74.956  | 76.821  | 81.946  | 94.736  | 87.196  | 139.244 | 277.587 |

| 2500000 | 46.327 | 61.770  | 80.342  | 84.864  | 87.657  | 89.807  | 95.771  | 110.853 | 97.994  | 156.527 | 311.959 |

| 3000000 | 52.517 | 70.023  | 91.321  | 96.399  | 99.532  | 101.946 | 108.693 | 125.919 | 108.065 | 172.646 | 344.022 |

| 4000000 | 60.251 | 80.335  | 104.770 | 110.594 | 114.189 | 116.958 | 124.701 | 144.463 | 123.979 | 198.073 | 394.685 |

| 5000000 | 67.558 | 90.078  | 117.479 | 124.008 | 128.041 | 131.146 | 139.827 | 161.985 | 139.017 | 222.099 | 442.560 |

| 6000000 | 75.754 | 101.005 | 131.728 | 139.052 | 143.573 | 147.053 | 156.788 | 181.634 | 155.879 | 249.038 | 496.241 |

| 5LM     | I I    |         |         |         |         |         |         |         |         |         |         |

| 5000    | 1.101  | 2.131   | 3.631   | 4.856   | 5.667   | 6.669   | 7.466   | 10.397  | 27.238  | 43.360  | 75.830  |

| 10000   | 1.454  | 2.786   | 5.283   | 7.317   | 8.515   | 9.976   | 11.505  | 14.451  | 28.408  | 45.339  | 79.344  |

| 50000   | 3.982  | 7.834   | 11.818  | 15.670  | 15.961  | 17.081  | 19.976  | 21.666  | 33.760  | 45.929  | 80.374  |

| 100000  | 4.366  | 8.861   | 13.229  | 17.597  | 17.944  | 19.229  | 22.403  | 25.679  | 38.952  | 51.540  | 90.198  |

| 150000  | 12.201 | 16.268  | 20.336  | 21.549  | 22.420  | 23.081  | 24.701  | 28.244  | 37.837  | 60.488  | 120.977 |

| 200000  | 12.843 | 17.125  | 21.406  | 22.691  | 23.606  | 24.304  | 26.004  | 29.734  | 39.771  | 63.584  | 127.122 |

| 300000  | 14.128 | 18.839  | 23.546  | 25.259  | 26.216  | 26.944  | 28.801  | 32.903  | 43.955  | 70.178  | 140.207 |

| 400000  | 15.414 | 20.549  | 25.509  | 27.257  | 28.353  | 29.181  | 31.225  | 35.606  | 47.515  | 75.722  | 151.247 |

| 500000  | 17.195 | 22.925  | 28.658  | 30.567  | 31.763  | 32.670  | 34.938  | 39.931  | 50.573  | 80.618  | 160.986 |

| 600000  | 18.406 | 24.543  | 30.852  | 32.862  | 34.119  | 35.073  | 37.494  | 42.926  | 52.025  | 82.947  | 165.605 |

| 800000  | 21.208 | 28.278  | 35.852  | 38.107  | 39.514  | 40.584  | 43.360  | 49.779  | 56.220  | 89.670  | 178.967 |

| 1000000 | 23.825 | 31.767  | 40.524  | 43.008  | 44.554  | 45.733  | 48.837  | 56.178  | 60.119  | 95.916  | 191.374 |

| 1500000 | 31.000 | 41.333  | 53.245  | 56.374  | 58.312  | 59.798  | 63.815  | 73.637  | 71.856  | 114.706 | 228.749 |

| 2000000 | 37.721 | 50.295  | 65.166  | 68.898  | 71.208  | 72.980  | 77.849  | 90.000  | 82.837  | 132.281 | 263.707 |

| 2500000 | 44.011 | 58.682  | 76.324  | 80.621  | 83.274  | 85.317  | 90.983  | 105.311 | 93.093  | 148.700 | 296.362 |

| 3000000 | 49.891 | 66.523  | 86.755  | 91.579  | 94.555  | 96.849  | 103.257 | 119.622 | 102.661 | 164.014 | 326.821 |

| 4000000 | 57.239 | 76.318  | 99.532  | 105.065 | 108.479 | 111.110 | 118.466 | 137.239 | 117.779 | 188.169 | 374.950 |

| 5000000 | 64.180 | 85.575  | 111.606 | 117.807 | 121.639 | 124.588 | 132.836 | 153.885 | 132.067 | 210.995 | 420.432 |

| 6000000 | 71.965 | 95.955  | 125.141 | 132.099 | 136.394 | 139.700 | 148.949 | 172.552 | 148.084 | 236.587 | 471.429 |

| 7000000 | 78.436 | 104.582 | 136.393 | 143.976 | 148.655 | 152.259 | 162.339 | 188.067 | 161.397 | 257.858 | 513.812 |

| 8000000 | 87.950 | 117.266 | 152.935 | 161.439 | 166.687 | 170.727 | 182.031 | 210.877 | 180.976 | 289.134 | 576.135 |

#### 1.5.2 TIMING PARAMETERS

This section discusses issues involving timing parameters.

#### 1.5.2.1 Transition Time

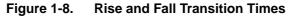

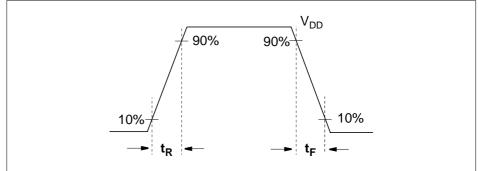

Figure 1-8. shows the definition of rise transition time ( $t_R$ ) and fall transition time ( $t_F$ ). Transition time is defined as the delay between the time when the input (output) signal voltage level is 10% of supply voltage ( $V_{DD}$ ) and the time of the input (output) signal voltage level is 90% of  $V_{DD}$ .

#### 1.5.2.2 Propagation Delays

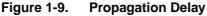

Figure 1-9. shows the definition of propagation delays. Propagation delay is defined as the delay between the time when the input signal voltage level is 50% of supply voltage (V<sub>DD</sub>) and the time when the output signal voltage level is 50% of V<sub>DD</sub>.

#### 1.5.2.3 Setup / Hold Time

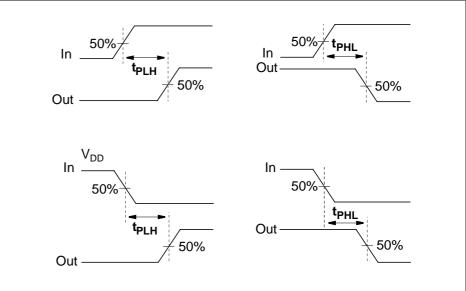

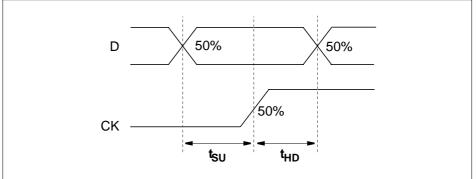

Figure 1-10. shows the definition of setup time and hold time. The setup timing check is defined as the minimum interval which a data signal must remain stable before active transition of a clock. Any change to the data signal within this interval results in a timing violation.

The hold timing check is defined as the minimum interval which a data signal must remain stable after active transition of a clock. Any change to the data signal within this interval results in a timing violation.

Figure 1-10. Setup and Hold Times

#### 1.5.2.4 Recovery Times

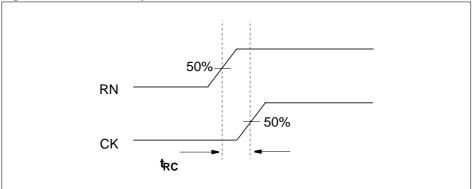

Figure 1-11. shows the definition of recovery time. A recovery timing check measures the time between the release of an asynchronous control signal from the active state to the next active clock edge.

For example, the time between RN and the CK of FD2 cell. If the active edge of the CK occurs too soon after the release of the RN, the state of the FD2 becomes uncertain. The state can be the value set by the RN or the value clocked into the FD2 from the data input.

#### 1.5.2.5 Removal Times

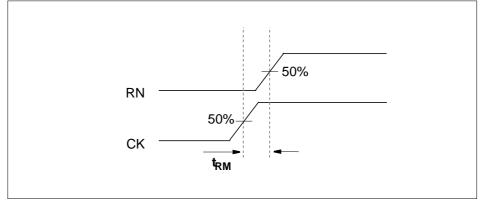

Figure 1-12. shows the definition of removal time. A removal timing check measures the time between the active clock edge and the release of an asynchronous control signal from the active state.

For example, the time between RN and the CK of FD2 cell. If the release of the RN occurs too soon after the active edge of the clock, the state of the FD2 becomes uncertain. The uncertainty can be caused by the value set by the RN or the value clocked into the FD2 from the data input.

Figure 1-12. Removal Time

#### 1.5.2.6 Minimum Pulse Widths

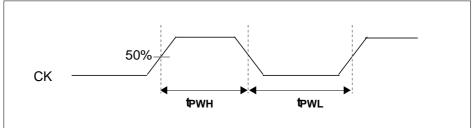

Figure 1-13. shows the definition of minimum pulse width. The minimum pulse width timing check is the minimum allowable time for the positive (high) or negative (low) phase of each cycle.

Figure 1-13. Minimum Pulse Width

#### 1.5.2.7 Minimum Period

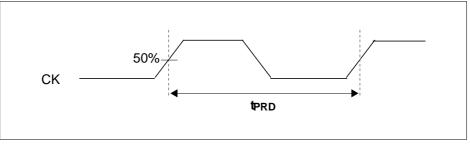

Figure 1-14. shows the definition of minimum period. The minimum period timing check is the minimum allowable time for one complete cycle of the signal.

#### Figure 1-14. Minimum Period

#### 1.5.3 TEMPERATURE AND SUPPLY VOLTAGE

The next figure describes propagation delay derating factors ( $K_T$ ,  $K_V$ ) as a function of on-chip junction temperature ( $T_J$ ) and supply voltage ( $V_{DD}$ ). As a result of power dissipation, the junction temperature is generally higher than the ambient temperature.

The temperature of the die inside the package (junction temperature, T<sub>J</sub>) is calculated using chip power dissipation and the thermal resistance to the ambient temperature ( $\theta_{JA}$ ) of the package. Information on package thermal performance can be obtained from SEC application engineers.

#### 1.5.4 BEST AND WORST CASE CONDITIONS

A circuit should be designed to operate properly within a given specification level, either commercial or industrial. It is recommended that circuits be simulated for best case, normal case, and worst case conditions at each specification level.

The following expressions also allow for the effect of process variation on circuit performance.

Best case(Worst case):

$T_{BC}$  ( $T_{WC}$ ) =  $K_P \times K_T \times K_V \times T_{NOM}$

where

$T_{BC}$  = Best case propagation delay

$T_{WC}$  = Worst case propagation delay

T<sub>NOM</sub> = Normal propagation delay

$(T_{\rm J} = 25^{\rm o}$ C,  $V_{\rm DD} = 2.5$ V and typical process)

$\mathbf{K}_{P}$   $\mathbf{K}_{T}$ ,  $\mathbf{K}_{V}$  = Refer to Table 1-2., Table 1-3., and Table 1-4.

#### 1.5.5 DERATING FACTORS OF STD110

The multipliers can be applied to nominal delay data in order to estimate the effects of supply voltage, temperature and process. Nominal data are provided for conditions of  $V_{DD} = 2.5 \text{ V}$ ,  $T_J = 25 \,^{\circ}\text{C}$  and typical process.

The derating factors of STD110 is as follows.

| Table 1-2. | STD110 cell process derating factor (K <sub>P</sub> ) |

|------------|-------------------------------------------------------|

|------------|-------------------------------------------------------|

| Process Factor (K <sub>P</sub> ) | Slow  | Тур | Fast  |

|----------------------------------|-------|-----|-------|

|                                  | 1.212 | 1.0 | 0.841 |

#### Table 1-3.STD110 cell temperature derating factor (K<sub>T</sub>)

| Temp. ( <sup>o</sup> C) | 125   | 85    | 70    | 25    | 0     | -40   |

|-------------------------|-------|-------|-------|-------|-------|-------|

| K <sub>T</sub>          | 1.143 | 1.086 | 1.065 | 1.000 | 0.964 | 0.906 |

Table 1-4.STD110 cell voltage derating factor (K<sub>V</sub>)

| Voltage (V)    | 2.3   | 2.5   | 2.7   |

|----------------|-------|-------|-------|

| K <sub>V</sub> | 1.075 | 1.000 | 0.940 |

| 1.6         | The ASIC timing characteristics consist of the following components:   |

|-------------|------------------------------------------------------------------------|

| Delay Model | Cell propagation delay from input to output transitions based on input |

and capacitance.

- Interconnection wire delay across the metal lines.

- Timing requirement parameters such as setup time, hold time, recovery time, skew time, minimum pulse width, etc.

waveform slope, fanout loads and distributed interconnection wire resistance

• Derating factors for junction temperature, power supply voltage, and process variations.

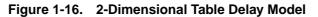

Timing model for STD110 focuses on how to characterize cell propagation delay time accurately. To accomplish this goal, 2-dimensional table look-up delay model has been adopted. The index variables of this table are input waveform slope and output load capacitance. See the figure below. SEC ASIC design automation system supports an n-dimensional table model even though we adopted 2-dimensional model for our  $0.25 \mu m$  cell-based products.

The Table 1-5. shows an example of this model for 2-input NAND cell. The data in this table are high-to-low transition delay times from one of the two input pins to output pin. The number of points and values of the index variables can differ for each cell.

| SLOP \ CAP | 0.0050  | 0.0220  | 0.3030  | 0.5840  |

|------------|---------|---------|---------|---------|

| 0.0200     | 0.03644 | 0.07275 | 0.66481 | 1.25660 |

| 0.1700     | 0.05508 | 0.09725 | 0.68658 | 1.27820 |

| 1.5850     | 0.07719 | 0.16698 | 0.92337 | 1.49790 |

| 3.0000     | 0.06421 | 0.17730 | 1.10970 | 1.74950 |

Table 1-5.Table Delay Model Example

Notice that 4-by-4 table is used. Delay values between grid points and beyond this table are determined by linear interpolation and extrapolation methods. This general table delay model provides great flexibility as well as high accuracy since extensive software revisions are not required when a cell library is updated. The other timing components such as interconnection wire delay, timing requirement parameters and derating factors are characterized in a commonly-accepted way in industry.

The figure below summarizes the features of SEC ASIC's delay model.

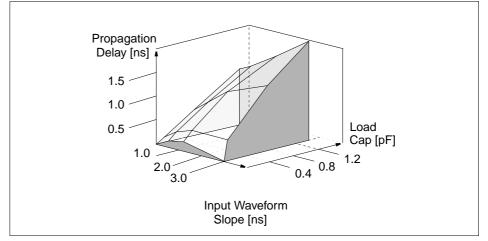

- ① 2-dimensional table delay model for output loading and input waveform slope effects is used. The slopes  $(t_R, t_F)$  and delay times  $(t_{PLH}, t_{PHL})$  of all cell instances are calculated recursively.

- ② The input waveform slope of each primary input pad and the loading capacitance of each primary output pad can be assigned individually or by default.

- ③ Pin to pin delays of cells and interconnection wires are supported.

- ④ The effect of distributed interconnection wire resistance and capacitance on cell delay is analysed using the effective capacitance concept.

Figure 1-17. Features of Delay Model

| 1.7                                  | 1.7.1 SCAN DESIGN                                                                                                                                                                                                                                                   |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Testability<br>Design<br>Methodology | <ul> <li>Multiplexed scan flip-flop that minimizes the area or delay overhead needed to implement scan design.</li> <li>Automated design rules checking, scan insertion, and test pattern generation</li> <li>High fault coverage on synchronous designs</li> </ul> |

|                                      | 1.7.2 BOUNDARY-SCAN                                                                                                                                                                                                                                                 |

#### • IEEE Std 1149.1

- JTAG boundary-scan registers with primitive cells

- Boundary-Scan Description Language (BSDL) description for board testing

- Combination with internal scan design and core testing

#### Boundary Scan Architecture

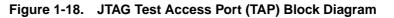

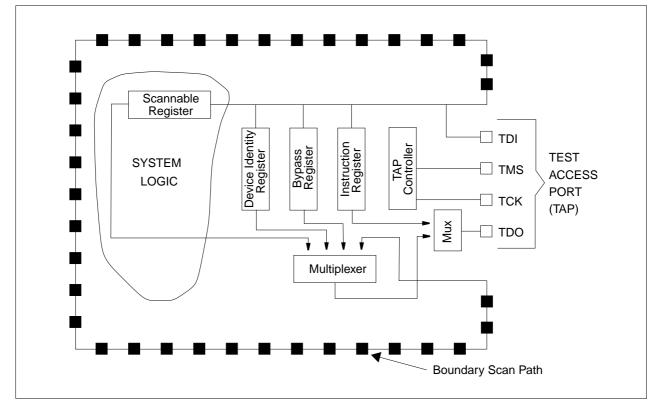

A boundary scan architecture contains TAP (Test Access Port), TAP controller, instruction register and a group of test data registers. The instruction and test data registers are separate shift-register-based paths connected in parallel with a common serial data input and a common serial data output which are connected to TAP, TDI and TDO signals. TAP controller selects the alternative instruction and test data register paths between TDI and TDO. The schematic view of the top level design of the test logic architecture is shown in the Figure 1-18.

#### **Boundary Scan Functional Block Descriptions**

#### TAP (Test Access Port)

TAP is a general-purpose port that can provide with an access to many test support functions built into a component, including the test logic. It includes three inputs (TCK; Test Clock Signal, TMS; Test Mode Signal and TDI; Test Data Input) and one output (TDO; Test Data Output) required by the test logic. An optional fourth input (TRSTN; Test Reset) is provided for the asynchronous initialization of the test logic. The values applied at TMS and TDI pins are sampled on the rising edge of TCK, and the value placed on TDO pin changes on the falling edge of TCK.

#### **TAP Controller**

TAP controller receives TCK, interprets the signals on TMS, and generates clock and control signals for both instruction and test data registers and for other parts of the test circuitries as required.

#### Instruction Register/Instruction Decoder

Test instructions are shifted into and held by the instruction register. Test instructions include a selection of tests to be performed or the test data register to be accessed. A basic 3-bit instruction register and its instruction decoder are provided as macrofunctions in the library.

#### **Test Data Registers**

Data registers include a bypass register, a boundary scan register, a device identification register and other design specific registers. Only the bypass- and boundary scan registers are mandatory; the rest are optional.

| Bypass register: The bypass register<br>the circuit when none of the other<br>can be used to allow test data to<br>other components in a product w                                                                                                                                                                                                                                                                           | r test data regist<br>flow through a g | ers is selected. It iven device to the |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|

| Boundary scan register: The boundary scan register detects typical production defects in<br>board interconnects, such as opens, shorts, etc. It also allows an<br>access to component inputs and outputs when you test their logic or<br>sample flow-through signals. Special boundary scan register<br>macrocells are provided for this purpose. These special registers is<br>discussed in the next section of next pages. |                                        |                                        |

| Design-specific test data register: These optional registers may be provided to allow an access to<br>design-specific test support features in the integrated circuit, such as<br>self-test, scan test.                                                                                                                                                                                                                      |                                        |                                        |

| Device identification register: This is a<br>number and variant of a compone<br>identification register is partitione                                                                                                                                                                                                                                                                                                        | ents to be identif                     |                                        |

| Device version identifier1st field                                                                                                                                                                                                                                                                                                                                                                                           | The first four bi                      | ts beginning from MSB                  |

| Device part number                                                                                                                                                                                                                                                                                                                                                                                                           | 2nd field                              | 16 bits                                |

| Manufacturer's JEDEC number                                                                                                                                                                                                                                                                                                                                                                                                  | 3rd field                              | 11 bits                                |

| LSB                                                                                                                                                                                                                                                                                                                                                                                                                          | 4th field                              | 1 bit —tied in High                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |                                        |

The ASIC designer is free to fill the version and part number in any manner as long as the total twenty bits are used.

SEC's JEDEC code: 78 decimal = 1001110 Continuation field (4 bits) = 0000

Contents of device identification register:

#### 1.7.3 BIST (BUILT-IN SELF-TEST)

- · Efficient test solution for compiled memory macrocells

- At speed and parallel testing of multiple memories

- Less routing overhead and test pin requirements

## 1.8 Maximum Fanouts

#### 1.8.1 INTERNAL MACROCELLS

The maximum fanouts for STD110 primitive cells are as follows. Note that these fanout limitation values are calculated when the rise and fall times of the input signal is 0.213 ns. Depending on the rise and fall times, the maximum fanout limitations can be varied case by case.

In the following table the maximum fanout values for all pins of STD110 internal macrocells are listed.

# Table 1-6.Maximum Fanoutsof Internal Macrocells

(When input  $t_R/t_F = 0.213$ ns, one fanout (SL) = 0.006710pF)

| Cell     | Output | Maximum |

|----------|--------|---------|

| Name     | Pin    | Fanouts |

| ad2      | Y      | 48      |

| ad2d2    | Y      | 97      |

| ad2d4    | Y      | 190     |

| ad2dh    | Y      | 21      |

| ad3      | Y      | 48      |

| ad3d2    | Y      | 94      |

| ad3d4    | Y      | 188     |

| ad3dh    | Y      | 21      |

| ad4      | Y      | 48      |

| ad4d2    | Y      | 94      |

| ad4d4    | Y      | 185     |

| ad4dh    | Y      | 21      |

| ad5      | Y      | 23      |

| ad5d2    | Y      | 46      |

| ad5d4    | Y      | 190     |

| ao21     | Y      | 22      |

| ao211    | Y      | 14      |

| ao2111   | Y      | 9       |

| ao2111d2 | Y      | 97      |

| ao211d2  | Y      | 28      |

| ao211d2b | Y      | 97      |

| ao211d4  | Y      | 195     |

| ao211dh  | Y      | 7       |

| ao21d2   | Y      | 45      |

| ao21d2b  | Y      | 95      |

| ao21d4   | Y      | 192     |

| ao21dh   | Y      | 10      |

| ao22     | Y      | 22      |

| ao221    | Y      | 13      |

| ao221d2  | Y      | 95      |

| ao221d4  | Y      | 192     |

| ao222    | Y      | 13      |

| ao2222   | Y      | 8       |

| ao2222d2 | Y      | 95      |

| ao2222d4 | Y      | 192     |

| ao222a   | Y      | 20      |

| ao222d2  | Y      | 25      |

| ao222d2a | Y      | 95      |

| ao222d2b | Y      | 95      |

| ao222d4  | Y      | 191     |

| ao222d4a | Y      | 192     |

| ao22a    | Y      | 22      |

| Cell               | Output   | Maximum   |

|--------------------|----------|-----------|

| Name               | Pin      | Fanouts   |

| ao22d2             | Y        | 43        |

| ao22d2a            | Y        | 43        |

| ao22d2b            | Ý        | 96        |

| ao22d2b            | Y        | 191       |

| ao22d4a            | Y        | 191       |

| ao22dh             | Y        | 9         |

| ao22dha            | Y        | 9         |

|                    | Y        | 21        |

| ao31               | ř<br>Y   |           |

| ao311              | -        | 13        |

| ao3111             | Y        | 8         |

| ao3111d2           | Y        | 97        |

| ao311d2            | Y        | 97        |

| ao311d4            | Y        | 191       |

| ao31d2             | Y        | 43        |

| ao31d4             | Y        | 194       |

| ao31dh             | Y        | 9         |

| ao32               | Y        | 20        |

| ao321              | Y        | 12        |

| ao321d2            | Y        | 95        |

| ao321d4            | Y        | 192       |

| ao322              | Y        | 11        |

| a0322d2            | Y        | 95        |

| a0322d2<br>a0322d4 | Y        | 192       |

| a032204<br>a032d2  | Y Y      | 97        |

|                    | •        | -         |

| ao32d4             | Y        | 191       |

| ao33               | Y        | 19        |

| ao331              | Y        | 11        |

| ao331d2            | Y        | 95        |

| ao331d4            | Y        | 193       |

| ao332              | Y        | 10        |

| ao332d2            | Y        | 95        |

| ao332d4            | Y        | 192       |

| ao33d2             | Y        | 95        |

| ao33d4             | Y        | 190       |

| ao4111             | Ý        | 8         |

| ao4111d2           | Y        | 95        |